# Narrow VDC Regulator/Charger with SMBus Interface and Internal Switching FETs

## **ISL9519C**

The ISL9519C is a highly integrated Narrow VDC system voltage regulator and battery charger controller. Operating parameters are programmable over the System Management Bus (SMBus). The ISL9519C is designed for applications where the system power source is either the battery pack or the output of the regulator/charger. This makes the max voltage to the system equal to the max battery voltage instead of the max adapter voltage. The ISL9519C also includes a patented system to control trickle charging deeply discharged batteries while maintaining system voltage at a user defined minimum. High efficiency is achieved with a DC/DC synchronous-rectifier buck converter, equipped with diode emulation and variable switching frequency for enhanced light load efficiency and AC-adapter boosting prevention. The ISL9519C can charge one, two or three series connected Lithium-ion cells, at up to 8A charge current. Default settings for 1-, 2- or 3-cell operation at power-up are selected by an external pin. Integrated MOSFETs. drivers and bootstrap diode result in fewer components and smaller implementation area. Low offset current-sense amplifiers provide high accuracy.

The ISL9519C provides an open drain digital output that indicates the presence of the AC-adapter. The ISL9519C also provides an analog output that indicates the adapter current.

# **Applications**

- Notebook Computers

- Tablet PCs

- · Portable Equipment with Rechargeable Batteries

## **Features**

- ±0.5% System Voltage Accuracy (-10°C to +100°C)

- ±3% Accurate Input Current Limit

- ±3% Accurate Battery Charge Current Limit

- Variable Switching Frequency at Light Load Conditions for Higher Efficiency

- · Fixed Frequency Operation at Higher Loads

- Fixed Frequency Mode can be Forced by an External Pin

- · Trickle Charge System for Deeply Discharged Batteries

- Automatic Trickle Charge Current (256mA)

- Holds Minimum Voltage to System

- · SMBus 2-Wire Serial Interface

- Default System Voltage Values for 1-Cell, 2-Cell or 3-Cell Operation Selected by an External Pin

- · Adapter In-rush FET Control

- Adapter Isolation FET Control

- Battery Short Circuit Protection

- · Fast System-Load Transient Response

- · Monitor Outputs

- Adapter Current (2.5% Accuracy)

- AC-adapter Present Indicator

- 11-Bit Max System Voltage Setting

- · 7-Bit Min System Voltage Setting

- · 6-Bit Charge Current Setting

- Over 8A Battery Charger Current

- . 6-Bit Adapter Current Setting

- Over 8A Adapter Current

- +4.5V to +22V Adapter Voltage Range

- · Pb-Free (RoHS Compliant)

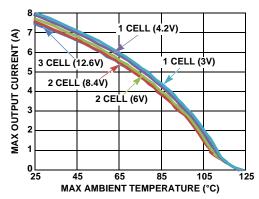

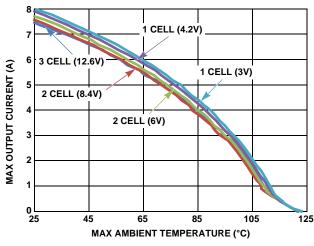

FIGURE 2. MAX LOAD CURRENT VS AMBIENT TEMPERATURE WITH 1M/S FORCED AIR COOLING

**TABLE 1. ISL9519 FAMILY**

| PART NUMBER | LOGIC LEVELS         | PIN 9 FUNCTION                    | DEFAULT ADAPTER<br>CURRENT LIMIT | INTERNAL<br>SWITCHING FETS |

|-------------|----------------------|-----------------------------------|----------------------------------|----------------------------|

| ISL9519     | 3.3V or 5V pull-up   | AMON<br>(Adapter Current Monitor) | 3.584A                           | NO                         |

| ISL9519C    | 3.3V or 5V pull-up   | AMON<br>(Adapter Current Monitor) | 3.584A                           | YES                        |

| ISL9519R    | 3.3V or 5V pull-up   | AMON<br>(Adapter Current Monitor) | 0.128A                           | NO                         |

| ISL9519Q    | 1.8V or 2.5V pull-up | CCMON<br>(Charge Current Monitor) | 3.584A                           | NO                         |

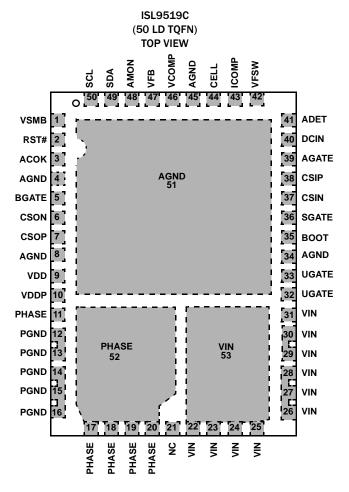

# **Pin Configuration**

# **Functional Pin Descriptions**

| PIN NUMBER | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                |

|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VSMB   | SMBus interface Supply Voltage Input. Bypass with a 0.1µF capacitor to AGND.                                                                                                                                                                                                               |

| 2          | RST#   | Logic input sets all SMBus registers to default values when low.                                                                                                                                                                                                                           |

| 3          | ACOK   | AC Detect Output. This open drain output is high impedance when ADET is greater than 3.2V. The ACOK output remains low when the ISL9519C is powered down. Connect a 10k pull-up resistor from ACOK to VSMB.                                                                                |

| 5          | BGATE  | Gate drive for the battery connection PFET. This pin can go high to disconnect the battery, low to connect the battery or operate in a linear mode to regulate minimum system voltage during trickle charge. It is also the compensation point for the Min System Voltage regulation loop. |

# Functional Pin Descriptions (Continued)

| PIN NUMBER                                       | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                              |

|--------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6                                                | CSON   | Charge Current-Sense Negative Input and system voltage feedback.                                                                                                                                                                                                                         |

| 7                                                | CSOP   | Charge Current-Sense Positive Input.                                                                                                                                                                                                                                                     |

| 4, 8, 34, 45, 51                                 | AGND   | Ground Connection for low power analog and digital circuits.                                                                                                                                                                                                                             |

| 9                                                | VDD    | Linear Regulator Output. VDD is the output of the 5.1V linear regulator supplied from DCIN. VDD supplies regulated power input for internal analog circuits. Connect a 4.7 $\Omega$ resistor from VDD to VDDP and a 1 $\mu$ F ceramic capacitor from VDD to AGND.                        |

| 10                                               | VDDP   | VDDP directly supplies the LGATE driver and the BOOT strap diode. Bypass with a $1\mu\text{F}$ ceramic capacitor from VDDP to PGND.                                                                                                                                                      |

| 11, 17, 18, 19, 20,<br>52                        | PHASE  | Switching Power Output. Connect to the inductor.                                                                                                                                                                                                                                         |

| 12, 13, 14, 15, 16                               | PGND   | Power Ground. Connect PGND to the system or power ground.                                                                                                                                                                                                                                |

| 21                                               | NC     | NC.                                                                                                                                                                                                                                                                                      |

| 22, 23, 24, 25, 26,<br>27, 28, 29, 30, 31,<br>53 | VIN    | High-Side Power MOSFET Drain. Connect to the Power input and decouple with low ESR capacitors to PGND.                                                                                                                                                                                   |

| 32, 33                                           | UGATE  | High-Side Power MOSFET Driver Output and the gate of the high side FET. Connect a 4700pF cap from UGATE to PHASE.                                                                                                                                                                        |

| 35                                               | воот   | High-Side Power MOSFET Driver Power-Supply Connection. Connect a 0.1µF capacitor from BOOT to PHASE.                                                                                                                                                                                     |

| 36                                               | SGATE  | System Gate PFET driver. Controls the Adapter Connection FET that blocks current flow from the battery to the adapter connector.                                                                                                                                                         |

| 37                                               | CSIN   | Adapter Current-Sense Negative Input.                                                                                                                                                                                                                                                    |

| 38                                               | CSIP   | Adapter Current-Sense Positive Input.                                                                                                                                                                                                                                                    |

| 39                                               | AGATE  | Adapter Gate (in-rush) FET control (open drain output).                                                                                                                                                                                                                                  |

| 40                                               | DCIN   | Charger Bias Supply Input. Bypass DCIN with a 0.1µF capacitor to AGND.                                                                                                                                                                                                                   |

| 41                                               | ADET   | AC-adapter Detection Input. Connect to a resistor divider from the AC-adapter output.                                                                                                                                                                                                    |

| 42                                               | VFSW   | Logic input enables Variable Frequency Switching at light loads.                                                                                                                                                                                                                         |

| 43                                               | ICOMP  | Output of the Current Control error amplifier.                                                                                                                                                                                                                                           |

| 44                                               | CELL   | Logic level input selects 1-cell, 2-cell or 3-cell default MaxSystemVoltage and MinSystemVoltage register values. Floating the cell pin selects 1-cell. Pulling CELL to VSMB selects 3-cell and pulling CELL low selects 2-cell defaults. The CELL pin is read only at VSMB POR or RST#. |

| 46                                               | VCOMP  | Output of the Voltage loop error amplifier.                                                                                                                                                                                                                                              |

| 47                                               | VFB    | Negative input to the Min System Voltage and Max System Voltage control error amplifier.                                                                                                                                                                                                 |

| 48                                               | AMON   | Input Current Monitor Output. AMON voltage equals 20 x (V <sub>CSIP</sub> - V <sub>CSIN</sub> ).                                                                                                                                                                                         |

| 49                                               | SDA    | SMBus Data I/O. Open-drain Output. Connect an external pull-up resistor according to SMBus specifications.                                                                                                                                                                               |

| 50                                               | SCL    | SMBus Clock Input. Connect an external pull-up resistor according to SMBus specifications.                                                                                                                                                                                               |

| 51                                               | AGND   | Connect the backside paddle to AGND and PGND (pins 8 and 12) and the system ground plane.                                                                                                                                                                                                |

# **Ordering Information**

| PART NUMBER  | PART         | TEMP RANGE  | PACKAGE       | PKG.     |

|--------------|--------------|-------------|---------------|----------|

| (Notes 1, 2) | MARKING      | (°C)        | (Pb-Free)     | DWG. #   |

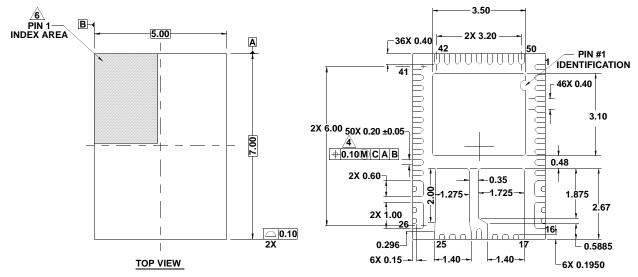

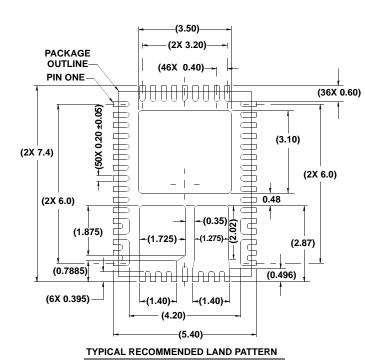

| ISL9519CHRZ  | ISL 9519CHRZ | -10 to +100 | 50 Ld 5x7 QFN | L50.5x7B |

## NOTES:

1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

intersil

- These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pbfree products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL9519C. For more information on MSL please see techbrief TB363.

# **Table of Contents**

| Functional Pin Descriptions                         | Setting Input Current Limit                   | 19   |

|-----------------------------------------------------|-----------------------------------------------|------|

| Absolute Maximum Ratings8                           | Control Register                              | 20   |

| Thermal Information                                 | Charger Timeout                               | 20   |

| Operating Conditions8                               | ISL9519C Data Byte Order                      | 20   |

| SMB Timing Specification                            | Writing to the Internal Registers             | 20   |

| Typical Operating Performance                       | Reading from the Internal Registers           | 20   |

| Theory of Operation                                 | Application Information                       | 20   |

| Introduction                                        | Inductor Selection                            | . 20 |

| PWM Control                                         | Output Capacitor Selection                    | . 21 |

| AC-Adapter Detection14                              | Snubber Design                                | 21   |

| <b>VDD Regulator</b>                                | Input Capacitor Selection                     | 21   |

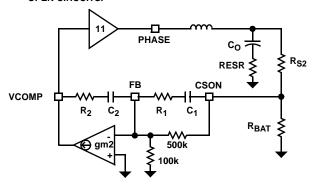

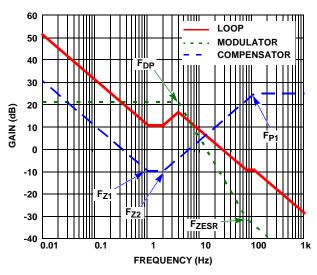

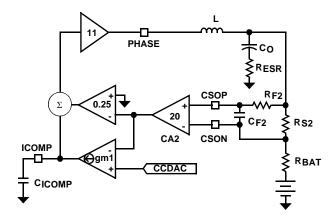

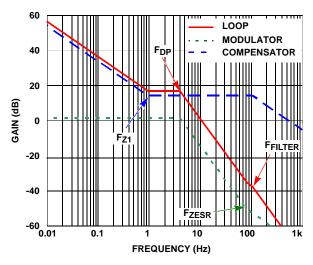

| VSMB Supply14                                       | Loop Compensation Design                      | 21   |

| Current Measurement                                 | Transconductance Amplifiers                   |      |

| SGATE Function                                      | gm1, gm2, gm3 and gm4                         | 21   |

| AGATE Function                                      | PWM Gain Fm                                   | 21   |

| BGATE Function                                      | Output LC Filter Transfer Functions           | . 22 |

| Trickle Charging14                                  | Max System Voltage Control Loop               | 22   |

| Short Circuit Protection and OV Battery Charging 14 | Compensation Break Frequency Equations        | . 22 |

| Over-Temperature Protection                         | Charge Current Control Loop                   | . 23 |

| The System Management Bus                           | Adapter Current Limit Control Loop            | . 24 |

| General SMBus Architecture                          | Min System Voltage Control Loop               | 24   |

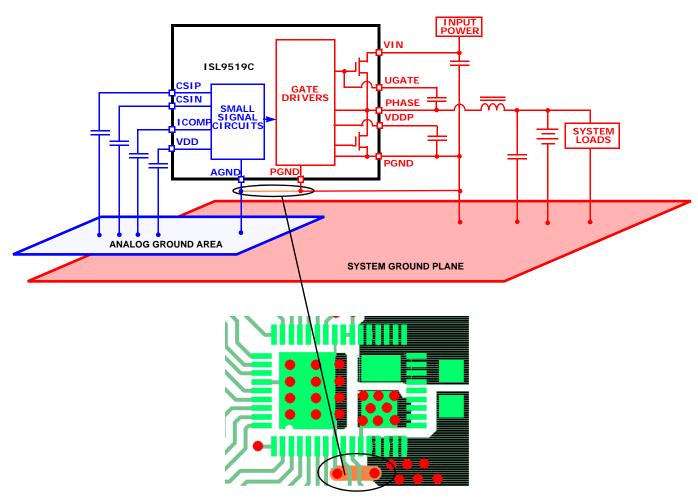

| Data Validity                                       | Guidelines for Layout and Component Placement | 24   |

| START and STOP Conditions                           | VIN (Input Power) Capacitors                  | . 25 |

| Acknowledge                                         | VDDP                                          | . 25 |

| SMBus Transactions                                  | UGATE                                         | 25   |

| Byte Format                                         | PHASE                                         | . 25 |

| ISL9519C and SMBus                                  | Copper Size for the Phase Node                | 25   |

| SMBus Registers                                     | B00T                                          | . 26 |

| Setting Max System Voltage                          | VDD                                           | . 26 |

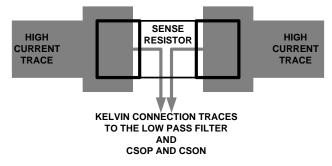

| Smart Battery Registers                             | CSOP, CSON, CSIP and CSIN                     | 26   |

| Max Accepted Max System Voltage Command 17          | Revision History                              | 27   |

| Setting Minimum System Voltage                      | Products                                      | 27   |

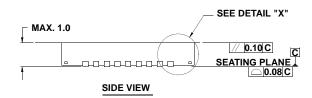

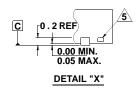

| BGATE and 1 Cell Operation                          | Package Outline Drawing                       | 28   |

| Setting Charge Current                              |                                               |      |

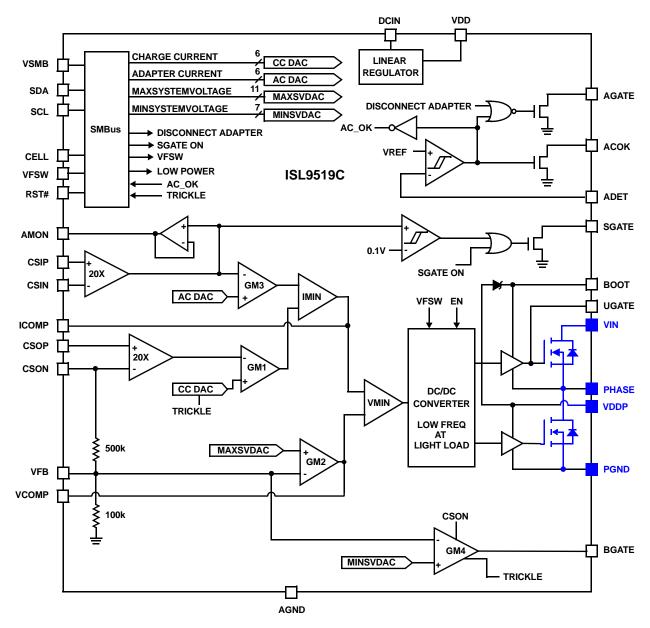

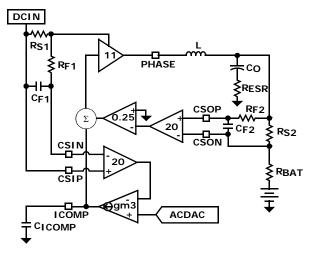

FIGURE 3. FUNCTIONAL BLOCK DIAGRAM

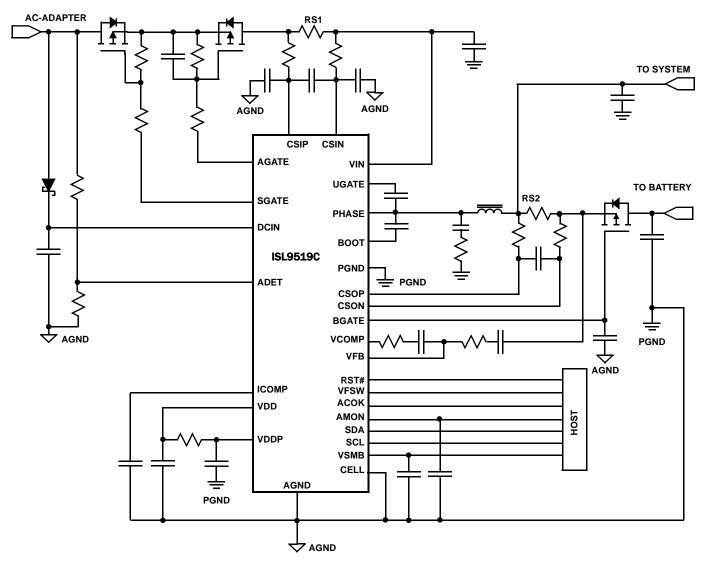

FIGURE 4. TYPICAL APPLICATION CIRCUIT

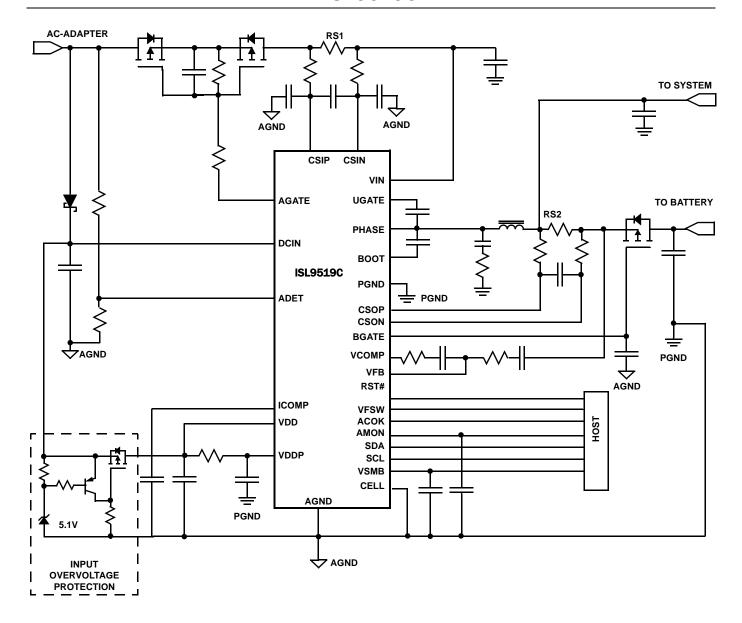

FIGURE 5. TYPICAL 5V INPUT APPLICATION CIRCUIT

## **Absolute Maximum Ratings**

| DCIN, CSIP, CSON, AGATE               | 0.3V to +28V                                          |

|---------------------------------------|-------------------------------------------------------|

| CSIP-CSIN, CSOP-CSON, PGND-AGND       | 0.3V to +0.3V                                         |

| BOOT Voltage (V <sub>BOOT-GND</sub> ) | 0.3V to 33V                                           |

| BOOT To PHASE Voltage (VBOOT-PHASE)   | 0.3V to 7V                                            |

| PHASE Voltage (Note 4)                |                                                       |

| UGATE Voltage                         | . V <sub>PHASE</sub> - 0.3V (DC) to V <sub>BOOT</sub> |

| AMON, ICOMP, VCOMP, VFB               | 0.3V to VDD + 0.3V                                    |

| VSMB, SCL, SDA                        | 0.3V to +6V                                           |

| ADET, ACOK, CELL, VFSW, RST#          | 0.3V to +6V                                           |

| VDDP, VDD to AGND, VDDP to PGND       | 0.3V to +6V                                           |

| BGATE                                 | . AGND - 0.3V to CSON + 0.3V                          |

| CELL                                  | 0.3V to VSMB + 0.3V                                   |

## **Thermal Information**

| Thermal Resistance (Typical)            | $\theta_{JA}(^{\circ}C/W)$ | $\theta_{JC}$ (°C/W) |

|-----------------------------------------|----------------------------|----------------------|

| 50 Ld TQFN Package (Notes 5, 6)         | 32                         | 2                    |

| Operating Junction Temperature Range    | 10                         | 0°C to +125°C        |

| Storage Temperature                     | 6                          | 5°C to +150°C        |

| Pb-Free Reflow Profile                  |                            | see link below       |

| http://www.intersil.com/pbfree/Pb-FreeR | <u>leflow.asp</u>          |                      |

## **Operating Conditions**

| Temperature Range (see Figure 8) | 10°C to +100°C |

|----------------------------------|----------------|

|----------------------------------|----------------|

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. The Phase Voltage is capable of withstanding -7V when the BOOT pin is at GND.

- 5. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 6. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** DCIN = CSIP = CSIN = 19V, CSOP = CSON = 12V, VDDP = 5V, VSMB = 3.42V, BOOT-PHASE = 5V, AGND = PGND = 0V, CVDD =  $1\mu$ F,  $T_A = -10$  °C to +100 °C. Boldface limits apply over the operating temperature range, -10 °C to +100 °C.

| PARAMETER                       | CONDITIONS                                                                                                                                                                                                                                                                                   | MIN<br>(Note 8) | TYP    | MAX<br>(Note 8) | UNITS |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|-----------------|-------|

| SYSTEM VOLTAGE REGULATION       | ·                                                                                                                                                                                                                                                                                            |                 | •      |                 |       |

| Maximum System Voltage Accuracy | MaxSystemVoltage = 0x3130                                                                                                                                                                                                                                                                    | 12.529          | 12.592 | 12.655          | ٧     |

|                                 |                                                                                                                                                                                                                                                                                              | -0.5            |        | 0.5             | %     |

|                                 | MaxSystemVoltage = 0x20D0                                                                                                                                                                                                                                                                    | 8.358           | 8.4    | 8.442           | ٧     |

|                                 |                                                                                                                                                                                                                                                                                              | -0.5            |        | 0.5             | %     |

|                                 | MaxSystemVoltage = 0x1060                                                                                                                                                                                                                                                                    | 4.171           | 4.192  | 4.213           | ٧     |

|                                 |                                                                                                                                                                                                                                                                                              | -0.5            |        | 0.5             | %     |

| Minimum System Voltage Accuracy | MinSystemVoltage = 0x2400                                                                                                                                                                                                                                                                    | 8.940           | 9.216  | 9.492           | ٧     |

|                                 |                                                                                                                                                                                                                                                                                              | -3              |        | 3               | %     |

|                                 | MinSystemVoltage = 0x1800                                                                                                                                                                                                                                                                    | 5.898           | 6.144  | 6.390           | V     |

|                                 |                                                                                                                                                                                                                                                                                              | -4              |        | 4               | %     |

|                                 | MinSystemVoltage = 0x0C00                                                                                                                                                                                                                                                                    | 2.888           | 3.072  | 3.256           | ٧     |

|                                 |                                                                                                                                                                                                                                                                                              | 6               |        | 6               | %     |

| CHARGE CURRENT REGULATION       |                                                                                                                                                                                                                                                                                              |                 |        |                 |       |

| Charge Current and Accuracy     | RS2 = $10m\Omega$ (see Figure 4)                                                                                                                                                                                                                                                             | 7.822           | 8.064  | 8.306           | Α     |

|                                 | ChargingCurrent = 0x1f80                                                                                                                                                                                                                                                                     | -3              |        | 3               | %     |

|                                 | RS2 = $10m\Omega$ (see Figure 4)                                                                                                                                                                                                                                                             | 3.973           | 4.096  | 4.219           | Α     |

|                                 | ChargingCurrent = 0x1000                                                                                                                                                                                                                                                                     | -3              |        | 3               | %     |

|                                 | RS2 = 10mΩ (see Figure 4)<br>ChargingCurrent = 0x0100                                                                                                                                                                                                                                        | 166             | 256    | 346             | mA    |

| Trickle Charge Current          | RS2 = $10m\Omega$ (see Figure 4) CSON-BGATE < 4.3V or BGATE < 1V                                                                                                                                                                                                                             | 166             | 256    | 346             | mA    |

| Trickle Charge Threshold        | CSON-BGATE                                                                                                                                                                                                                                                                                   | 4.0             | 4.7    | 5.5             | V     |

| Battery Quiescent Current       | I <sub>CSOP</sub> + I <sub>CSON</sub> + I <sub>PHASE</sub> + I <sub>CSIP</sub> + I <sub>CSIN</sub> + I <sub>AGATE</sub> V <sub>PHASE</sub> = V <sub>BOOT</sub> = V <sub>CSON</sub> = V <sub>CSOP</sub> = V <sub>CSIP</sub> = V <sub>AGATE</sub> = 12.6V, V <sub>DCIN</sub> = VDD = VDDP = 0V |                 | 14     | 25              | μΑ    |

**Electrical Specifications** DCIN = CSIP = CSIN = 19V, CSOP = CSON = 12V, VDDP = 5V, VSMB = 3.42V, BOOT-PHASE = 5V, AGND = PGND = 0V, CVDD =  $1\mu$ F,  $T_A$  = -10 °C to +100 °C. **Boldface limits apply over the operating temperature range, -10 °C to +100 °C. (Continued)**

| PARAMETER                                | conditions                                                         | MIN<br>(Note 8) | TYP  | MAX<br>(Note 8) | UNITS |

|------------------------------------------|--------------------------------------------------------------------|-----------------|------|-----------------|-------|

| INPUT CURRENT REGULATION                 |                                                                    |                 |      |                 |       |

| Input Current Accuracy                   | RS1 = 20mΩ (see Figure 4)<br>Adapter Current = 512mA               | -7              |      | 7               | %     |

|                                          | RS1 = 20mΩ (see Figure 4)<br>Adapter Current = 4096mA or 8064mA    | -3              |      | 3               | %     |

| CSIP/CSIN Input Voltage Range            |                                                                    | 5               |      | 26              | ٧     |

| AMON Accuracy                            | V <sub>CSIP-CSIN</sub> = 161.28mV, AMON load < 1μA                 | -2.5            |      | 2.5             | %     |

| Ideal AMON = 20*(CSIP-CSIN)              | V <sub>CSIP-CSIN</sub> = 81.92mV AMON load < 1μA                   | -4              |      | 4               | %     |

|                                          | V <sub>CSIP-CSIN</sub> = 10.24mV, AMON load < 1μA                  | -20             |      | 20              | %     |

|                                          | V <sub>CSIP-CSIN</sub> = 5.12mV, AMON load < 1μA                   | -40             |      | 40              | %     |

| AMON Min Output Voltage                  | V <sub>CSIP-CSIN</sub> = 0.0V, AMON load < 1μA                     |                 | 30   | 80              | mV    |

| AMON Max Source Current                  | V <sub>CSIP-CSIN</sub> = 161.28mV, V <sub>AMON</sub> = 0V          | 25              | 40   | 60              | μΑ    |

| AMON Max Sink Current                    | V <sub>CSIP-CSIN</sub> = 0.0V, V <sub>AMON</sub> = 2V              | 25              | 40   | 60              | μΑ    |

| SUPPLY AND LINEAR REGULATOR              |                                                                    | 1               |      | •               |       |

| DCIN, Input Voltage Range                |                                                                    | 6               |      | 26              | ٧     |

| DCIN Quiescent Current                   | V <sub>ADAPTER</sub> = 5.5V to 26V, V <sub>BATTERY</sub> 4V to 16V |                 | 2    | 5               | mA    |

| VDD Output Voltage                       | 6.0V < V <sub>DCIN</sub> < 26V, no load                            | 4.975           | 5.1  | 5.23            | ٧     |

| VDD Load Regulation                      | 0 < I <sub>VDDP</sub> < 30mA (see note 6)                          |                 | 35   |                 | mV    |

| VDD UVLO Rising                          |                                                                    | 3.93            | 4.0  | 4.12            | ٧     |

| VDD UVLO Hysteresis                      |                                                                    | 170             | 235  | 325             | mV    |

| VSMB Range                               |                                                                    | 2.7             |      | 5.5             | ٧     |

| VSMB UVLO Rising                         |                                                                    | 2.5             | 2.75 | 2.95            | V     |

| VSMB UVLO Hysteresis                     |                                                                    | 75              | 125  | 175             | mV    |

| VSMB Quiescent Current                   | VSMB = SCL = SDA = 3.42V                                           |                 | 30   | 50              | μΑ    |

| VSMB Quiescent Current                   | VSMB = SCL = SDA = 3.42V, LOW POWER BIT = 1                        |                 | 14   | 25              | μΑ    |

| ADET                                     |                                                                    | <u> </u>        |      |                 |       |

| ADET Rising Threshold                    |                                                                    | 3.15            | 3.2  | 3.25            | ٧     |

| ADET Threshold Hysteresis                |                                                                    | 35              | 60   | 90              | mV    |

| ADET Input Leakage Current               |                                                                    |                 |      | 1               | μΑ    |

| ACOK                                     |                                                                    |                 |      |                 |       |

| Sink Current                             | V <sub>ACOK</sub> = 0.4V, ADET = 2.7V                              | 2               | 8    |                 | mA    |

| Leakage Current                          | V <sub>ACOK</sub> = 5.5V, ADET = 3.7V                              |                 |      | 1               | μΑ    |

| AGATE                                    |                                                                    |                 |      |                 |       |

| Sink Current                             | V <sub>ADET</sub> > 3.5V, AGATE = 0.4V                             | 1               | 2.3  |                 | mA    |

| Leakage Current                          | V <sub>ADET</sub> = 0V, AGATE = 26V                                |                 |      | 1               | μA    |

| SGATE                                    |                                                                    | <u>l</u>        |      |                 |       |

| CSIP-CSIN Threshold for SGATE Going High |                                                                    |                 | 6.6  | 9               | mV    |

| CSIP-CSIN Threshold Hysteresis           |                                                                    | 1.5             | 3.3  |                 | mV    |

| Sink Current                             | CSIP-CSIN > 10mV, AGATE = 0.4V                                     | 1               | 2.3  |                 | mA    |

| Leakage Current                          | CSIP-CSIN = 0V, AGATE = 26V                                        |                 |      | 1               | μA    |

**Electrical Specifications** DCIN = CSIP = CSIN = 19V, CSOP = CSON = 12V, VDDP = 5V, VSMB = 3.42V, BOOT-PHASE = 5V, AGND = PGND = 0V, CVDD =  $1\mu$ F,  $T_A = -10^{\circ}$ C to  $+100^{\circ}$ C. Boldface limits apply over the operating temperature range,  $-10^{\circ}$ C to  $+100^{\circ}$ C. (Continued)

| PARAMETER                            | CONDITIONS                                                    | MIN<br>(Note 8) | TYP  | MAX<br>(Note 8) | UNITS         |

|--------------------------------------|---------------------------------------------------------------|-----------------|------|-----------------|---------------|

| VFSW                                 |                                                               |                 |      | "               |               |

| VFSW Input Low Voltage               |                                                               |                 |      | 0.8             | ٧             |

| VFSW Input High Voltage              |                                                               | 2               |      |                 | ٧             |

| VFSW Input Leakage Current           |                                                               |                 |      | 1               | μΑ            |

| RST#                                 |                                                               | 1               |      | 1               | 1             |

| Input Low Voltage                    | VSMB = 2.7V to 5.5V                                           |                 |      | 0.8             | V             |

| Input High Voltage                   | VSMB = 2.7V to 5.5V                                           | 2               |      |                 | V             |

| Input Leakage Current                | VSMB = 2.7V to 5.5V                                           |                 |      | 1               | μΑ            |

| BATTERY CELL SELECTOR                |                                                               | 1               |      |                 |               |

| CELL Input Voltage for 3-Cell Select |                                                               | VSMB<br>-0.4    |      |                 | V             |

| CELL Input Voltage for 1-Cell Select |                                                               | 0.85            |      | VSMB<br>-1.2    | V             |

| CELL Input Voltage for 2-Cell Select |                                                               |                 |      | 0.4             | V             |

| CELL Input Current Lo                | CELL = GND, RST# = GND                                        | -40             |      |                 | μΑ            |

| CELL Input Current Hi                | CELL = VSMB, RST# = GND                                       |                 |      | 40              | μΑ            |

| CELL Float Voltage                   | CELL = Open, RST# = GND                                       |                 | 1.23 |                 | ٧             |

| CELL Input Current Hi Z              | CELL = 0V or VSMB, RST# = VSMB                                |                 | 0.05 | 1               | μΑ            |

| SWITCHING REGULATOR                  |                                                               | ,               |      | -11             | .1            |

| Frequency 400kHz                     | Register 0x3D = xx1x0x00b                                     | 330             | 400  | 440             | kHz           |

| Max Variable Frequency               | Register 0x3D = xx1x1x0xb, CCM load                           | 330             | 400  | 440             | kHz           |

| Min Variable Frequency 1             | Register 0x3D = xx1x1x0xb, no load                            |                 | 140  |                 | kHz           |

| Min Variable Frequency 2             | Register 0x3D = xx1x1x1xb, no load                            |                 | 80   |                 | kHz           |

| ERROR AMPLIFIERS                     |                                                               | ,               |      | -11             | .1            |

| gm2 Amplifier Transconductance       | Transconductance from VFB to VCOMP                            | 200             | 250  | 300             | μ <b>A</b> /V |

| gm1 Amplifier Transconductance       | Transconductance from (CSOP-CSON) to ICOMP                    | 40              | 50   | 60              | μ <b>A</b> /V |

| gm3 Amplifier Transconductance       | Transconductance from (CSIP-CSIN) to ICOMP                    | 40              | 50   | 60              | μ <b>A</b> /V |

| gm4 Amplifier Transconductance       | Transconductance from VFB to BGATE                            | 50              | 100  | 150             | μ <b>A</b> /V |

| gm1/gm3 Saturation Current           |                                                               | 15              | 21   | 25              | μΑ            |

| gm2 Saturation Current               |                                                               | 10              | 17   | 25              | μΑ            |

| ICOMP, VCOMP Clamp Voltage           | Max Voltage between V <sub>VCOMP</sub> and V <sub>ICOMP</sub> | 200             | 300  | 400             | m۷            |

| LOGIC LEVELS                         |                                                               | ,               |      | -11-            | .1            |

| SDA/SCL Input Low Voltage            | VSMB = 2.7V to 5.5V                                           |                 |      | 0.8             | V             |

| SDA/SCL Input High Voltage           | VSMB = 2.7V to 5.5V                                           | 2               |      |                 | V             |

| SDA/SCL Input Bias Current           | VSMB = 2.7V to 5.5V                                           |                 |      | 1               | μΑ            |

| SDA, Output Sink Current             | V <sub>SDA</sub> = 0.4V                                       | 4               | 12   |                 | mA            |

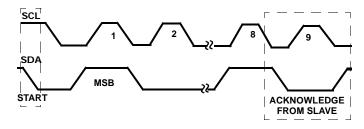

## **SMB Timing Specification** VSMB = 2.7V to 5.5V.

| PARAMETERS      | SYMBOL           | CONDITIONS | MIN<br>(Note 8) | TYP | MAX<br>(Note 8) | UNITS |

|-----------------|------------------|------------|-----------------|-----|-----------------|-------|

| SMBus Frequency | FSMB             |            | 10              |     | 100             | kHz   |

| Bus Free Time   | t <sub>BUF</sub> |            | 4.7             |     |                 | μs    |

## **SMB Timing Specification** VSMB = 2.7V to 5.5V. (Continued)

| PARAMETERS                           | SYMBOL              | CONDITIONS                                                                                        | MIN<br>(Note 8) | TYP | MAX<br>(Note 8) | UNITS |

|--------------------------------------|---------------------|---------------------------------------------------------------------------------------------------|-----------------|-----|-----------------|-------|

| Start Condition Hold Time from SCL   | t <sub>HD:STA</sub> |                                                                                                   | 4               |     |                 | μs    |

| Start Condition Set-up Time from SCL | t <sub>SU:STA</sub> |                                                                                                   | 4.7             |     |                 | μs    |

| Stop Condition Set-up Time from SCL  | t <sub>SU:STO</sub> |                                                                                                   | 4               |     |                 | μs    |

| SDA Hold Time from SCL               | t <sub>HD:DAT</sub> |                                                                                                   | 300             |     |                 | ns    |

| SDA Set-up Time from SCL             | t <sub>SU:DAT</sub> |                                                                                                   | 250             |     |                 | ns    |

| SCL Low Period                       | t <sub>LOW</sub>    |                                                                                                   | 4.7             |     |                 | μs    |

| SCL High Period                      | t <sub>HIGH</sub>   |                                                                                                   | 4               |     |                 | μs    |

| SMBus Inactivity Time-out            |                     | Maximum Charging Period Without a SMBus<br>Write to MaxSystemVoltage or ChargeCurrent<br>Register | 120             | 180 | 250             | S     |

#### NOTES:

- 7. Limits should be considered typical and are not production tested.

- 8. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

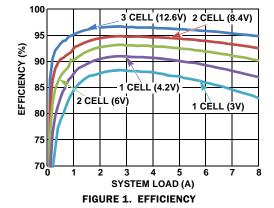

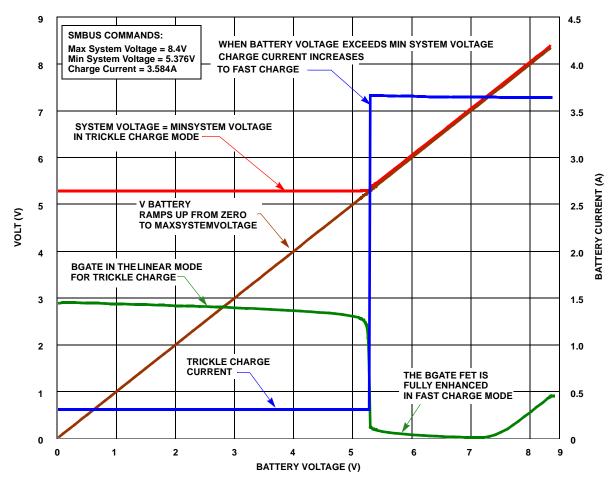

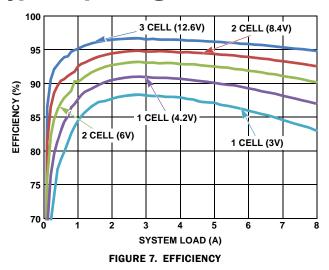

# Typical Operating Performance DCIN = 20V, 2S2P Li-Battery, T<sub>A</sub> = +25 °C, unless otherwise noted.

FIGURE 6. CHARGE CURRENT AND SYSTEM VOLTAGE VS BATTERY VOLTAGE

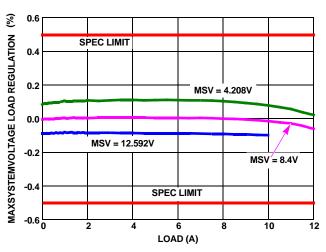

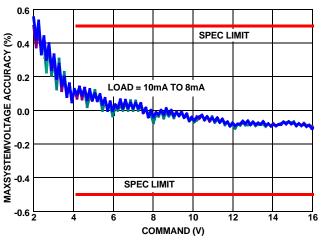

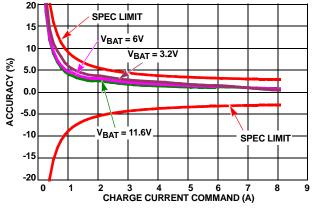

# Typical Operating Performance DCIN = 20V, 2S2P Li-Battery, T<sub>A</sub> = +25 °C, unless otherwise noted. (Continued)

FIGURE 8. MAX LOAD CURRENT VS AMBIENT TEMPERATURE WITH 1M/S FORCED AIR COOLING

FIGURE 10. MAXSYSTEMVOLTAGE COMMAND ACCURACY

FIGURE 11. CHARGE CURRENT COMMAND ACCURACY

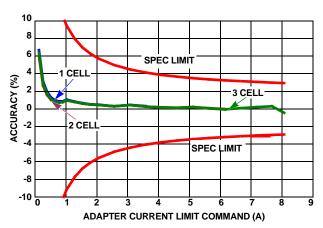

FIGURE 12. ADAPTER CURRENT LIMIT ACCURACY

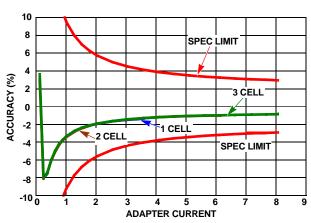

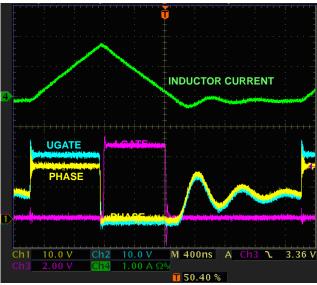

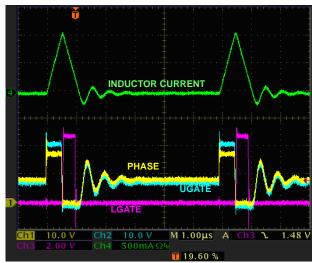

# Typical Operating Performance DCIN = 20V, 2S2P Li-Battery, T<sub>A</sub> = +25 °C, unless otherwise noted. (Continued)

FIGURE 13. AMON ACCURACY

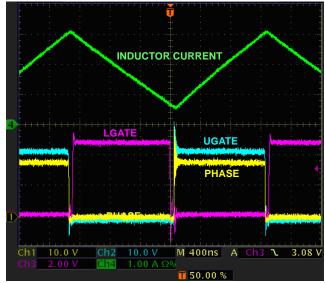

FIGURE 15. SWITCHING WAVEFORMS IN DISCONTINUOUS CONDUCTION MODE (LGATE IS INTERNAL)

# **Theory of Operation**

## Introduction

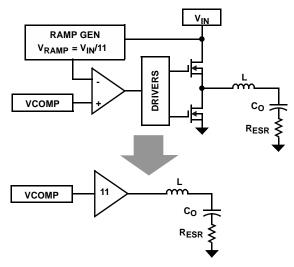

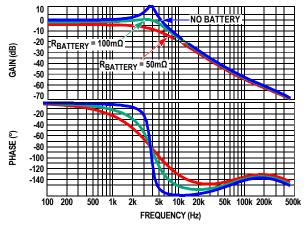

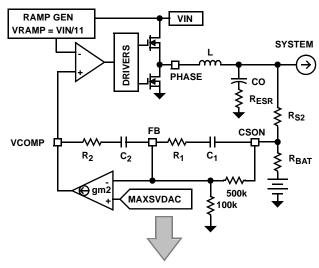

A high efficiency synchronous buck converter is used to control the system voltage up to 16.368V and charging current up to 6A. The ISL9519C also has input current limiting up to 8.064A (or higher with lower values of sense resistor). The Input current limit, charge current limit, minimum and maximum system voltage are set by internal registers written with SMBus. The ISL9519C "Typical Application Circuit" on page 6 is depicted in Figure 4.

The ISL9519C charges the battery with constant charge current, set by the ChargeCurrent register, until the battery voltage rises to a voltage set by the MaxSystemVoltage register. The charger will then operate at a constant voltage. The adapter current is

FIGURE 14. LIGHT LOAD, LOW FREQUENCY SWITCHING WAVEFORMS (LGATE IS INTERNAL)

FIGURE 16. SWITCHING WAVEFORMS IN CONTINUOUS CONDUCTION MODE (LGATE IS INTERNAL)

monitored and if the adapter current rises to the limit set by the InputCurrent register, system voltage and battery charge current are reduced to limit adapter current. If battery voltage is below the min system voltage, the trickle charge system is activated.

The ISL9519C features two voltage regulation loops and two current regulation loops. The max system voltage loop controls the voltage at CSON with a precision voltage divider to the voltage error amplifier GM2. The min system voltage prevents the system voltage from dropping below a minimum value even if a deeply discharged battery is inserted that is below the minimum. The Charge Current regulation loop limits the battery charging current delivered to the battery to ensure that it never exceeds the current set by the ChargeCurrent register. The Input Current regulation loop limits the current drawn from the AC-adapter to ensure that it never exceeds the limit set by the InputCurrent register to prevent adapter overload.

#### **PWM Control**

The ISL9519C employs a variable frequency pulse width modulator (PWM) with feed-forward. The switching frequency is constant in Continuous Conduction Mode (CCM) but is reduced in Discontinuous Mode (DCM). Switching frequency can be fixed by setting bits in the control register and/or pulling the VFSW pin

#### **AC-Adapter Detection**

AC-adapter voltage is connected through a resistor divider to ADET to detect when AC power is available, as shown in Figure 4. ACOK is an open-drain output and is active low when ADET is less than V<sub>th.fall</sub>, and high Z when ADET is above V<sub>th.rise</sub>. The ADET rising threshold is 3.2V (typ) with 57mV hysteresis. ADET must be above the threshold to enable the output voltage.

## **VDD Regulator**

VDD provides a 5.1V supply voltage from the internal LDO regulator from DCIN and can deliver up to 30mA of continuous current. VDD also supplies power to VDDP through a low pass filter, as shown in the "Typical Application Circuit" on page 6 in Figure 4. The MOSFET drivers are powered by VDDP. Bypass VDDP and VDD with a 1µF capacitor.

#### **VSMB Supply**

The VSMB input provides power to the SMBus interface. Connect an external supply to VSMB to keep the SMBus interface active while the supply to DCIN is removed. When VSMB is biased, the internal registers are maintained. Bypass VSMB to AGND with a 0.1µF or greater ceramic capacitor.

## **Current Measurement**

AMON is an output voltage that is proportional to the adapter current being sensed across CSIP and CSIN. The output voltage range is 0.1V to 3.2V. The voltage of AMON is given by Equation 1:

$$AMON = 20 \cdot I_{INPUT} \cdot R_{S1}$$

(EQ. 1)

Where I<sub>INPUT</sub> is the DC current drawn from the AC-adapter. A capacitor is required at the AMON output to stabilize the AMON amplifier and to minimize switching noise.

#### **SGATE Function**

SGATE is the System Isolation FET. The SGATE pin pulls low to turn an external PFET ON when current flowing from the adapter to the system exceeds a threshold (see "Electrical Specifications" table on page 9). SGATE is high (open drain) when the adapter current drops below the threshold. When the SGATE FET is OFF, its body diode blocks current flow from the system to the adapter connector.

#### **AGATE Function**

AGATE controls the Adapter Isolation FET. The AGATE pin pulls low to turn an external PFET ON when adapter voltage is above a threshold set by resistor divider to ADET. AGATE is high (open drain) when ADET is less than 3.2V. When the AGATE FET is OFF, its body diode blocks current flow from the adapter to the system. A capacitor between the gate and source of the AGATE FET can slow the turn-on of the FET and reduce in-rush current. The AGATE FET can be forced OFF by the ISLOLATE\_ADAPTER bit in the control register.

#### **BGATE Function**

The BGATE pin drives the gate of an external PFET to control the minimum system voltage. If a battery is connected that is discharged below the value set in the MinSystemVoltage register, BGATE controls the system voltage at the value set in the MinSystemVoltage register.

## **Trickle Charging**

If a battery that is discharged below the value set in the MinSystemVoltage register is connected to the system, the trickle charge system is activated. In trickle charge mode, the charge current is reduced to 256mA. The value in the ChargeCurrent register is not changed. The BGATE FET is controlled in a linear mode to regulate the system voltage at min system voltage and to drop voltage between the min system voltage and the battery. This state is communicated to the host system by the trickle bit in the control register.

When the battery is charged to the min system voltage, the BGATE FET becomes fully enhanced and BGATE is pulled more than 4.5V below the system voltage or to ground in a 1-cell application. This changes the charge mode from trickle to fast charge. The charge current is increased to the value in the ChargeCurrent register. The trickle bit in the control register is set to 0.

## **Short Circuit Protection and 0V Battery** Charging

If a battery is connected that is completely discharged or a short circuit, the trickle charge system is activated. The Charge Current is reduced to 256mA and BGATE controls the BGATE FET to maintain system voltage at the value in the MinSystemVoltage register.

#### **Over-Temperature Protection**

If the die temperature exceeds +150°C, it turns both of the synchronous buck FETs off. The system bus and the battery charging are disabled. Once the die temp drops below +125°C, system bus regulation and battery charging will start-up again.

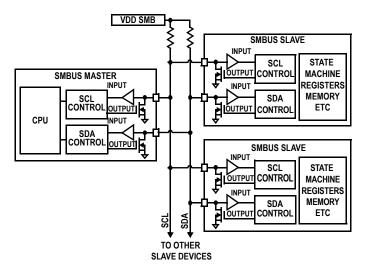

## **The System Management Bus**

The System Management Bus (SMBus) is a 2-wire bus that supports bidirectional communications. The protocol is described briefly here. More detail is available from http://www.smbus.org.

#### **General SMBus Architecture**

FIGURE 17.

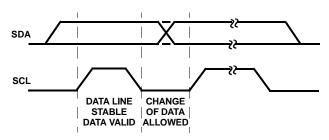

## **Data Validity**

The data on the SDA line must be stable during the HIGH period of the SCL, unless generating a START or STOP condition. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. Refer to Figure 18.

FIGURE 18. DATA VALIDITY

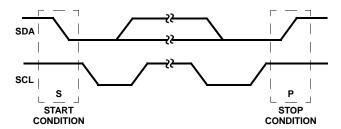

#### **START and STOP Conditions**

As shown in Figure 19, START condition is a HIGH to LOW transition of the SDA line while SCL is HIGH.

The STOP condition is a LOW to HIGH transition on the SDA line while SCL is HIGH. A STOP condition must be sent before each START condition.

FIGURE 19. START AND STOP WAVEFORMS

## **Acknowledge**

Each address and data transmission uses 9-clock pulses. The ninth pulse is the acknowledge bit (ACK). After the start condition, the master sends 7 slave address bits and a  $R/\overline{W}$  bit during the next 8-clock pulses. During the ninth clock pulse, the device that recognizes its own address holds the data line low to acknowledge (as shown in Figure 20). The acknowledge bit is also used by both the master and the slave to acknowledge receipt of register addresses and data.

FIGURE 20. ACKNOWLEDGE ON THE SMBus

## **SMBus Transactions**

All transactions start with a control byte sent from the SMBus master device. The control byte begins with a Start condition, followed by 7-bits of slave address (0001001 for the ISL9519C) followed by the  $R/\overline{W}$  bit. The  $R/\overline{W}$  bit is 0 for a write or 1 for a read. If any slave devices on the SMBus bus recognize their address, they will acknowledge by pulling the serial data (SDA) line low for the last clock cycle in the control byte. If no slaves exist at that address or are not ready to communicate, the data line will be 1, indicating a Not Acknowledge condition.

Once the control byte is sent, and the ISL9519C acknowledges it, the 2nd byte sent by the master must be a register address byte such as 0x14 for the ChargeCurrent register. The register address byte tells the ISL9519C which register the master will write or read. See Table 2 for details of the registers. Once the ISL9519C receives a register address byte it responds with an acknowledge.

#### WRITE TO A REGISTER REGISTER LO BYTE HI RYTE SI AVE s ADDR + W ADDR DATA DATA **READ FROM A REGISTER** REGISTER SLAVE SLAVE LO BYTE HI BYTE ADDR + W **ADDR** ADDR + R DATA DATA START **ACKNOWLEDGE** DRIVEN BY THE MASTER

FIGURE 21. SMBus/ISL9519C READ AND WRITE PROTOCOL

NO ACKNOWLEDGE

#### **TABLE 2. ISL9519C REGISTER SUMMARY**

| REGISTER<br>ADDRESS | REGISTER NAME    | READ/WRITE    | DESCRIPTION                     | ISL9519C<br>(1-CELL)<br>POR STATE | ISL9519C<br>(2-CELL)<br>POR STATE | ISL9519C<br>(3-CELL)<br>POR STATE |

|---------------------|------------------|---------------|---------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

| 0x14                | ChargeCurrent    | Read or Write | 6-Bit Charge Current Setting    | 0x0000 = 0A                       | 0x0000 = 0A                       | 0x0000 = 0A                       |

| 0x15                | MaxSystemVoltage | Read or Write | 11-Bit MaxSystemVoltage Setting | 0x1000 = 4.096V                   | 0x2000 = 8.192V                   | 0x3000 = 12.288V                  |

| 0x3D                | Control          | Read or Write | 8-Bit Control bit register      | 0x0000                            | 0x0000                            | 0x0000                            |

| 0x3E                | MinSystemVoltage | Read or Write | 7-Bit MinSystemVoltage Setting  | 0x0C00 = 3.072V                   | 0x1800 = 6.144V                   | 0x2400 = 9.216V                   |

| 0x3F                | InputCurrent     | Read or Write | 6-Bit Input Current Setting     | 0x0E00 = 3.584A                   | 0x0E00 = 3.584A                   | 0x0E00 = 3.584A                   |

| 0xFE                | ManufacturerID   | Read Only     | Manufacturer ID                 | 0x0049                            | 0x0049                            | 0x0049                            |

| 0xFF                | DeviceID         | Read Only     | Device ID                       | 0x0003                            | 0x0003                            | 0x0003                            |

#### **Byte Format**

Every byte put on the SDA line must be 8-bits long and must be followed by an acknowledge bit. Data is transferred with the most significant bit first (MSB) and the least significant bit last (LSB). The LO BYTE data is transferred before the HI BYTE data.

STOP

### ISL9519C and SMBus

The ISL9519C receives control inputs from the SMBus interface. The serial interface complies with the SMBus protocols as documented in the ISL9519C system Management Bus Specification V1.1, which can be downloaded from <a href="http://www.smbus.org">http://www.smbus.org</a>. The ISL9519C uses the SMBus Read-Word and Write-Word protocols (see Figure 21) to communicate with the host system and a smart battery. The ISL9519C is an SMBus slave device and does not initiate communication on the bus. It responds to the 7-bit address 0b0001001\_(0x12).

Read address = 0b00010011 and

Write address = 0b00010010.

In addition, the ISL9519C has two identification (ID) registers: a 16-bit device ID register (0xFF) and a 16-bit manufacturer ID register (0xFE).

The data (SDA) and clock (SCL) pins have Schmitt-trigger inputs that can accommodate slow edges. Choose pull-up resistors for SDA and SCL to achieve rise times according to the SMBus

specifications. The ISL9519C is controlled by the data written to the registers described in Table 2.

**DRIVEN BY ISL9519C**

#### **SMBus Registers**

The ISL9519C supports 7 internal registers (described in Table 2) that use either Write-Word or Read-Word protocols (see Figure 21). ManufacturerID and DeviceID are "read only" registers and can be used to identify the ISL9519C. On the ISL9519C, ManufacturerID always returns 0x0049 (ASCII code for "I" for Intersil) and DeviceID always returns 0x0003.

## **Setting Max System Voltage**

Max system voltage is set by writing a valid 16-bit number to the 16-bit MaxSystemVoltage register. The ISL9519C ignores the first 4 LSBs and uses the next 11 bits to set the voltage DAC. The max system voltage range of the ISL9519C is limited by the number of cells selected at the CELL pin. The maximum accepted commands for 1, 2, and 3 cells are listed in Table 4. Numbers requesting max system voltage greater than the value in Table 4 are ignored. The SMBus communication is not acknowledged (NAK) and the MaxSystemVoltage register is unchanged. The minimum command is 1.024V. All numbers requesting max system voltage below 1.024V result in a voltage set point of zero, which turns off the regulator.

The trickle charge system is activated when the BGATE FET is in its active region. Fast charging is active when the BGATE FET is fully enhanced (CSON-BGATE > 4.5V OR BGATE < 0.8V).

TABLE 3. MAXSYSTEMVOLTAGE (REGISTER 0x15)

| BIT    | BIT NAME                     | DESCRIPTION                                                                        |

|--------|------------------------------|------------------------------------------------------------------------------------|

| 0 to 3 |                              | Not used.                                                                          |

| 4      | MaxSystemVoltage, MAXSVDAC 0 | 0 = Adds 0mV of charger voltage, 1 = Adds 16mV of charger voltage. 1024mV minimum  |

| 5      | MaxSystemVoltage, MAXSVDAC 1 | 0 = Adds 0mV of charger voltage, 1 = Adds 32mV of charger voltage. 1024mV minimum  |

| 6      | MaxSystemVoltage, MAXSVDAC 2 | 0 = Adds 0mV of charger voltage, 1 = Adds 64mV of charger voltage. 1024mV minimum  |

| 7      | MaxSystemVoltage, MAXSVDAC 3 | 0 = Adds 0mV of charger voltage, 1 = Adds 128mV of charger voltage. 1024mV minimum |

| 8      | MaxSystemVoltage, MAXSVDAC 4 | 0 = Adds 0mV of charger voltage, 1 = Adds 256mV of charger voltage. 1024mV minimum |

| 9      | MaxSystemVoltage, MAXSVDAC 5 | 0 = Adds 0mV of charger voltage, 1 = Adds 512mV of charger voltage. 1024mV minimum |

| 10     | MaxSystemVoltage, MAXSVDAC 6 | 0 = Adds 0mA of charger voltage. 1 = Adds 1024mV of charger voltage.               |

| 11     | MaxSystemVoltage, MAXSVDAC 7 | 0 = Adds 0mV of charger voltage. 1 = Adds 2048mV of charger voltage.               |

| 12     | MaxSystemVoltage, MAXSVDAC 8 | 0 = Adds 0mV of charger voltage. 1 = Adds 4096mV of charger voltage.               |

| 13     | MaxSystemVoltage, MAXSVDAC 9 | 0 = Adds 0mV of charger voltage. 1 = Adds 8192mV of charger voltage.               |

| 14     |                              | Not Used. Normally a 16384mV weight                                                |

| 15     |                              | Not used. Normally a 32768mV weight.                                               |

Upon initial power-up of the VSMB supply, the MaxSystemVoltage register is reset to the POR value in Table 3. Use the Write-Word protocol (Figure 21) to write to the MaxSystemVoltage register. The register address for MaxSystemVoltage is 0x15. The 16-bit binary number formed by D15-D0 represents the max system voltage set point in mV. However, the resolution of the ISL9519C is 16mV because the D0-D3 bits are ignored, as shown in Table 3. The D14 and D15 bits are ignored because they are not needed to span the accepted range. Table 3 shows the mapping between the 16-bit number written to the MaxSystemVoltage register and max system voltage set point. The MaxSystemVoltage register can be read back to verify its contents.

#### **Smart Battery Registers**

The MaxSystemVoltage and ChargeCurrent registers use addresses and the format defined in the Smart Battery Charger Specification (Level 2) for ChargeVoltage and ChargeCurrent. In some systems, the Smart Battery Pack may write commands to these registers in ISL9519C. If a Smart Battery is used with ISL9519C, please refer to the Smart Battery Charger Specification for details.

# Max Accepted Max System Voltage Command

Commands that produce system voltage far higher than normal cell voltage are ignored. The max accepted MaxSystemVoltage commands depend on the CELL pin. Table 4 gives the maximum command that is accepted for 1, 2 and 3 cells.

**TABLE 4. MAX ACCEPTED MAX SYSTEM VOLTAGE COMMAND**

| # OF CELLS          | MAX ACCEPTED COMMAND | MIN IGNORED<br>COMMAND |

|---------------------|----------------------|------------------------|

| 1 (CELL = floating) | 0x17F0 (6.128V)      | 0x1800                 |

| 2 (CELL = GND)      | 0x27F0 (10.224V)     | 0x2800                 |

| 3 (CELL = VSMB)     | 0x3FF0 (16.368V)     | 0x4000                 |

# **Setting Minimum System Voltage**

Minimum System Voltage is set by writing a valid 16-bit number to the MinSystemVoltage register. This 16-bit number translates to a 65.535V full-scale voltage. The ISL9519C ignores the first 8 LSBs and uses the next 7 bits to set the MinSystemVoltage DAC. The minimum system voltage range of the ISL9519C is 0V to 19.2V. Numbers requesting minimum system voltage greater than 19.2V result in a minimum system voltage of 19.2V.

Upon initial power-up of the VSMB supply, the MinSystemVoltage register is reset to the POR value in Table 3. Use the Write-Word protocol (Figure 21) to write to the MinSystemVoltage register. The register address for MinSystemVoltage is 0x3E. The 16-bit binary number formed by D15-D0 represents the min system voltage set point in mV. However, the resolution of the ISL9519C is 256mV because the D0-D7 bits are ignored, as shown in Table 5. The D15 bit is also ignored because it is not needed to span the 0V to 19.2V range. Table 5 shows the mapping between the 16-bit number written to the MinSystemVoltage register and the min system voltage set point. The MinSystemVoltage register can be read back to verify its contents.

#### TABLE 5. MIN SYSTEM VOLTAGE (REGISTER 0x3E)

| BIT    | BIT NAME                     | DESCRIPTION                                                                           |

|--------|------------------------------|---------------------------------------------------------------------------------------|

| 0 to 7 |                              | Not used.                                                                             |

| 8      | MinSystemVoltage, MINSVDAC 0 | 0 = Adds 0mV of charger voltage, 1024mV minimum<br>1 = Adds 256mV of charger voltage. |

| 9      | MinSystemVoltage, MINSVDAC 1 | 0 = Adds 0mV of charger voltage, 1024mV minimum<br>1 = Adds 512mV of charger voltage. |

| 10     | MinSystemVoltage, MINSVDAC 2 | 0 = Adds 0mA of charger voltage.<br>1 = Adds 1024mV of charger voltage.               |

| 11     | MinSystemVoltage, MINSVDAC 3 | 0 = Adds 0mV of charger voltage.<br>1 = Adds 2048mV of charger voltage.               |

| 12     | MinSystemVoltage, MINSVDAC 4 | 0 = Adds 0mV of charger voltage.<br>1 = Adds 4096mV of charger voltage.               |

| 13     | MinSystemVoltage, MINSVDAC 5 | 0 = Adds 0mV of charger voltage.<br>1 = Adds 8192mV of charger voltage.               |

| 14     | MinSystemVoltage, MINSVDAC 6 | Not used.                                                                             |

| 15     | -                            | Not used.                                                                             |

#### TABLE 6. CHARGECURRENT (REGISTER 0x14) (10m $\Omega$ SENSE RESISTOR, RS2)

| BIT      | BIT NAME                | DESCRIPTION                                                                                              |

|----------|-------------------------|----------------------------------------------------------------------------------------------------------|

| 0 to 6   |                         | Not used.                                                                                                |

| 7        | Charge Current, CCDAC 0 | $0$ = Adds 0mA of charger current. 1 = Adds 128mA of charger current. (RS2 = $10$ m $\Omega$ )           |

| 8        | Charge Current, CCDAC 1 | $0$ = Adds $0$ mA of charger current. $1$ = Adds $256$ mA of charger current. (RS2 = $10$ m $\Omega$ )   |

| 9        | Charge Current, CCDAC 2 | $0$ = Adds 0mA of charger current. 1 = Adds 512mA of charger current. (RS2 = $10$ m $\Omega$ )           |

| 10       | Charge Current, CCDAC 3 | $0$ = Adds 0mA of charger current. 1 = Adds 1024mA of charger current. (RS2 = $10$ m $\Omega$ )          |

| 11       | Charge Current, CCDAC 4 | $0$ = Adds 0mA of charger current. 1 = Adds 2048mA of charger current. (RS2 = $10$ m $\Omega$ )          |

| 12       | Charge Current, CCDAC 5 | 0 = Adds 0mA of charger current. 1 = Adds 4096mA of charger current, (RS2 = $10m\Omega$ ) 8064mA maximum |

| 13 to 15 |                         | Not used.                                                                                                |

# **BGATE and 1 Cell Operation**

When operating with a 1 cell battery, the BGATE FET must have a low threshold voltage (V<sub>TH</sub>) and low r<sub>DSON</sub> with V<sub>GS</sub> = 2.5V. The V<sub>GS</sub> at 256mA must be less than the programmed MinSystemVoltage -1.2V. For example, if the minimum system voltage is 3.072V, the BGATE FETs V<sub>GS</sub> at ID = 256mA must be less than 1.872V (i.e., 3.072V-1.2V).

If the BGATE FETs  $V_{TH}$  is over 2V, and the minimum system voltage is 3.072V, BGATE will pull below 1.2V in the linear mode, and may not switch ISL9519C to trickle charge current.

# **Setting Charge Current**

The ISL9519C has a 16-bit ChargeCurrent register that sets the battery charging current. The ISL9519C controls the charge current by controlling the CSOP-CSON voltage. The register's LSB translates to  $10\mu V$  at CSON-CSOP. With a  $10m\Omega$  charge current R<sub>sense</sub> resistor (RS2 in the "Typical Application Circuit" on page 6), the LSB translates to 1mA charge current. The ISL9519C ignores the first 7 LSBs and uses the next 6-bits to control the current DAC.

The charge-current range of the ISL9519C is 0A to 8.064A (using a  $10\text{m}\Omega$  current-sense resistor). All numbers requesting charge current above 8.064A result in a current setting of 8.064A. All numbers requesting charge current between 0mA to 128mA result in a current setting of 0mA. After initial power-up of VSMB, the ChargeCurrent register is reset to 0x0000, BGATE is high (BGATE FET is 0FF) and charging is disabled. To charge the battery, write a valid, non-zero number to the ChargeCurrent register. The ChargeCurrent register uses the Write-Word protocol (Figure 21). The register code for ChargeCurrent is 0x14 (0b00010100). Table 6 shows the mapping between the 16-bit ChargeCurrent number and the charge current set point. The ChargeCurrent register can be read back to verify its contents.

# **Setting Input Current Limit**

When the input current exceeds the set input current limit, the ISL9519C decreases the charge current to provide priority to system load current. As the system load rises, the available charge current drops linearly to zero. Higher system loads can be drawn from the battery. If the battery is not present, the system voltage is reduced to supply more system current at the same input current. The total input current can increase to the limit of the AC-adapter.

The internal amplifier compares the differential voltage between CSIP and CSIN to a scaled voltage set by the InputCurrent register. The total input current is a function of battery charge current, system load current,  $V_{OUT}$ ,  $V_{IN}$  and efficiency. The total input current can be estimated by Equation 2:

$$I_{INPUT} = (I_{SYSTEM} + I_{BATTERY}) \times V_{SYSTEM} / (\eta \times V_{INPUT})$$

(EQ. 2)

Where  $\eta$  is the efficiency of the DC/DC converter (typically 90% to 95%).

The ISL9519C has a 16-bit InputCurrent register that translates to a 1mA LSB and a 65.53A full scale current using a  $20m\Omega$  current-sense resistor (RS1 in Figure 4). Equivalently, the 16-bit Input Current number sets the voltage across CSIP and CSIN inputs in  $20\mu V$  per LSB increments. To set the input current limit, use the SMBus to write a 16-bit InputCurrent register using the data format listed in Table 7. The InputCurrent register uses the Write-Word protocol (see Figure 21). The register code for InputCurrent is 0x3F (0b00111111). The InputCurrent register can be read back to verify its contents.

The ISL9519C ignores the first 7 LSBs and uses the next 6-bits to control the input current DAC. The input current range of the ISL9519C is from 128mA to 8.064A. All 16-bit numbers requesting input current above 8.064A result in an input-current setting of 8.064A. The default input current limit setting at power on of VSMB is the POR value in Table 2 on page 16.

TABLE 7. INPUT CURRENT (REGISTER 0x3F) (20mΩ SENSE RESISTOR, RS1)

| BIT      | BIT NAME               | DESCRIPTION                                                                                          |  |

|----------|------------------------|------------------------------------------------------------------------------------------------------|--|

| 0 to 6   |                        | Not used.                                                                                            |  |

| 7        | Input Current, ACDAC 0 | 0 = Adds 0mA of input current. 1 = Adds 128mA of input current. (RS1 = 20mΩ)                         |  |

| 8        | Input Current, ACDAC 1 | 0 = Adds 0mA of input current. 1 = Adds 256mA of input current. (RS1 = 20mΩ)                         |  |

| 9        | Input Current, ACDAC 2 | 0 = Adds 0mA of input current. 1 = Adds 512mA of input current. (RS1 = $20m\Omega$ )                 |  |

| 10       | Input Current, ACDAC 3 | 0 = Adds 0mA of input current. 1 = Adds 1024mA of input current. (RS1 = $20m\Omega$ )                |  |

| 11       | Input Current, ACDAC 4 | 0 = Adds 0mA of input current. 1 = Adds 2048mA of input current. (RS1 = $20m\Omega$ )                |  |

| 12       | Input Current, ACDAC 5 | 0 = Adds 0mA of input current. 1 = Adds 4096mA of input current. (RS1 = $20m\Omega$ ) 8064mA maximum |  |

| 13 to 15 |                        | Not used.                                                                                            |  |

#### TABLE 8. CONTROL REGISTER (REGISTER 0x3D)

| BIT     | BIT NAME             | DESCRIPTION                                                                                                                                                    |

|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | S <sub>GATE</sub> ON | $S_{GATE}$ ON = 1 forces ISL9519C to turn the SGATE FET ON.<br>$S_{GATE}$ ON = 0 allows ISL9519C to turn SGATE OFF if adapter current in below a min threshold |

| 1       | 80kHz                | When ISL9519C is in variable frequency mode, 80kHz = 1 sets min frequency to 80kHz.<br>80kHz = 0 sets min frequency to 140kHz                                  |

| 2       | Isolate Adapter      | Isolate Adapter = 1 disconnects the adapter from the charger by making the AGATE pin HI Z. Default 0                                                           |